#### SPACEWIRE REMOTE TERMINAL CONTROLLER Session: SpaceWire Components Short Paper

Jørgen Ilstad, Wahida Gasti

European Space Agency, Postbus 299, NL-2200 AG Noordwijk, The Netherlands

Peter Sinander

Saab Space AB, SE-40515 Göteborg, Sweden

Sandi Habinc

Gaisler Research AB, Första Långgatan 19, SE-41327 Göteborg, Sweden E-mail: jorgen.ilstad@esa.int, wahida.gasti@esa.int, peter.sinander@space.se, sandi@gaisler.com

## 1. Introduction

ESA initiated the development of the SpW Remote Terminal Controller (SpW-RTC) ASIC within a global strategy context based on the following driving aspects:

- 1) Ensure ESA payload program development with a set of ASSP<sup>1</sup>s capable of answering most of the On-Board computing and control needs for the future decade.

- 2) Adopt new ASIC developments to ESA ASSP strategy to reduce development time and recurring cost.

- **3)** Ensure SpW nodes developed by ESA (i.e. component, module, unit...etc) to be easily integrated in ESA On-Board Distributed Computing and Control System.

Hence, the objective of this paper is threefold:

- To demonstrate that SpW-RTC development is fully in line with ESA strategy

- To demonstrate that the SpW-RTC design has functionalities that fulfils a great number of on-board needs.

- To announce the last phase of its development as the SpW-RTC is currently in its manufacturing and validation phase.

Thus, this paper summarises ESA strategy for the SpW-RTC development and it presents the resulting description of the ASIC. Focus on its multi-function aspects, low power and high performance capability is provided by presenting a set of applications and related architectures where the SpW-RTC is well suited. For the conclusion, ESA ASSPs development strategy is assessed for the SpW-RTC case and related methodology for the SpW-RTC validation is presented.

## 2. SpW-RTC and ESA strategy for On-Board ASSPs

For the development of the SpW-RTC, ESA initiative can be summarised as follows:

- 1) Review and synthesis of power computation and communication requirements extracted from a large survey of applications ranging from housekeeping data acquisition to on-board processing. In addition to this, requirements inherent to the component's ability to monitor without loss of key functionalities were added. The results lead to the SpW-RTC specification.

- 2) The SpW-RTC design took advantage of number of ESA technical developments such as: pre-validated IP cores (i.e. LEON2-FT SPARC V8 core, SpW codec, CAN core), prevalidated rad-tolerant technology developed for the AT697. Atmel will manufacture the ASIC in ATC18RHA technology.

- **3)** ESA is leading and funding SpW-RTC development suites (based on the RTC-SpW FPGA board developed by Gaisler Research) which encompass:

- SpW-RTC Development suite (H/W and S/W) [RD3], [RD6]

- SW tools mainly based on SpaceWire device driver for the remote terminal controller [RD4]

The RTC-FPGA development kit is already integrated and validated at system level through TOPNET<sup>2</sup> initiative and related EGSEs<sup>3</sup> with results demonstrated in this conference [RD7].

<sup>&</sup>lt;sup>1</sup> Application Specific Signal Processors

<sup>&</sup>lt;sup>2</sup> Techonology for Onboard Processing Networks with Extended Throughput

## 3. SpW-RTC Description

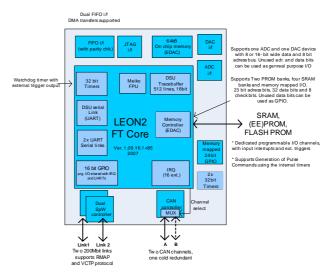

The SpW-RTC is a single chip embedded system, its architecture [RD1, RD2], is presented in figure 1 and provides the mixed capability to effectively perform data handling at platform level and powerful data processing at payload level.

Indeed it is judiciously based on:

- LEON2-FT SPARC V8 core with MEIKO FP unit.

- Appropriate amount of on-chip memory EDAC protected 64k SRAM, and EDAC protected interfaces to external memory devices such as SRAM, (EE) PROM.

- FIFO i/f (8 or 16 bit) with parity check.

- Two SpaceWire interfaces (compliant to SpW IP codec ECSS-E-50-12A and RMAP / ECSS-50-11 ) a Controller Area Network (CAN IP HurriCANe) bus controller

- ADC/DAC i/f (16bit) for payload data acquisition/conversion.

- Standard interfaces and resources (UARTs, 32bit timers, JTAG, general purpose input and output). It can provide up to 96 I/O lines as general purpose signals depending on its application.

Figure 1: Functional block diagram of the SpW-RTC

The SpW-RTC ASIC is entering the manufacturing stage as of Q3 2007 and ESA is expecting flight prototype by the end of the year.

## 4. SpW-RTC and On-Board Computing Architecture

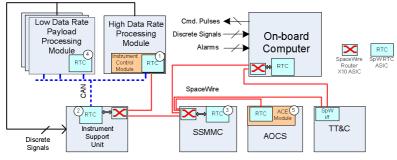

The SpW-RTC is a versatile high performance processor mainly designed for modular, reliable and fault-tolerant signal processing and on-board monitoring applications. Hence it is simultaneously maximising both communication aspects and processing power. It offers numerous configuration options considering its resources. Figure 2 illustrates some of its possible

applications within an On-Board Computing System. Following sections are detailing some of these examples showing that the SpW-RTC usage is not limited only to payload needs as it was intended in a first perspective but can also be extended to

Figure 2:SpW SpW-RTC in a distributed architecture.

platform demands as well. This list of examples is not exhaustive, but still instructive in terms of the SpW-RTCs capabilities, as other applications could be derived from these basic examples presented in this paper.

## 4.1 SpW-RTC usage in On-Board Computing & Control Modules

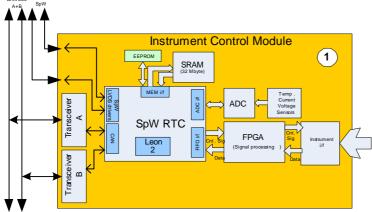

#### 4.1.1 Instrument Control Module

Instrument control needs to feature electronics for not only sensor control and monitoring but also data acquisition as well. The SpW-RTC is then the key component for such applications. Figure 3 illustrates how the SpW-RTC can be used as a part of the instrument control unit. High transfer

rates can be obtained due to the DMA capability between the SpaceWire interface and the FIFO interface.

One could envisage the LEON2 being used for TM packet generation which is buffered in SRAM and ultimately stored as files in the SSMM unit. The ICU can command and control the other instrument through the CAN bus

Figure 3: SpW-RTC embedded as a part of the ICU.

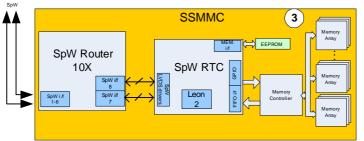

### 4.1.2 Solid State Mass Memory Controller (SSMMC)

Future ESA missions require significantly increased functionality and performance for the SSMM. Main requirements can be summarised as:

- To be able to handle a significant number of high speed SpW link simultaneously

- To be adaptable and configurable to different missions.

- To be able to support both payload and platform needs.

- To provide standard PUS<sup>4</sup> and SOIS<sup>5</sup> services at the application level for all types of memory access and control.

- To be able to implement SW file management services

- To easily upgrade capacity with memory chip technology improvement.

Figure 4:SpW-RTC embedded as a part of the SSMM

As represented in Figure 4, the SpW-RTC associated with a SpW\_10X router [RD5] can be a part of the core elements the SSMM controller. As indicated in the illustration on the left, the SpW-RTC might act as a protocol handler / file management device towards the memory controller sub system.

<sup>&</sup>lt;sup>4</sup> Packet Utilization Standard, ECSS-E-70-41A

<sup>&</sup>lt;sup>5</sup> Spacecraft Onboard Interface Services, CCSDS SOIS Draft Greenbook 850x0g0b

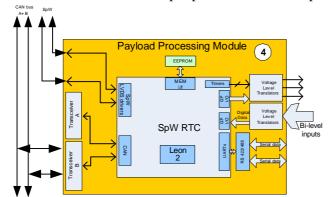

#### 4.1.3 Payload Processing Module

Figure 5 illustrates the SpW SpW-RTC being used in a digital module as a part of the payload processor module. General purpose I/O is used for discrete signalling and its UARTs are utilized to establish serial links with peripheral units. In this particular example, the SpW-RTC can largely

Figure 5:SpW-RTC embedded as a part of the PPM

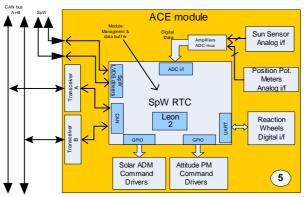

4.1.4 Attitude, Control Electronics Module

Figure 6: Attitude, Control Electronics Module

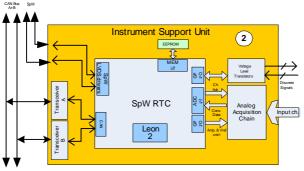

# 4.1.5 Instrument Support Unit

reduce its power consumption by reducing the system clock or the external clock SpW clock speed. The SpW codec allows for a receiving bit rate 7 times faster than the frequency of the SpW clock. The PLL used for SpW codec supports multiplication with factor 2 or 3. Selecting a 30 MHz SpW clock, still allows for reception of 200Mbps, while transmit rate is 60Mbps.

Figure 6 suggests how the SpW-RTC could be implemented in an attitude, control electronics module. Using the devices standard interfaces in conjunction with parallel interfaces offered by the applications GPIO, most can be accommodated for. Although the CAN bus in most cases is sufficient for command and control as well as data transfer, the SpaceWire links offers the added capability to remotely upload software using RMAP.

Monitoring of housekeeping parameters, both analog and digital, are typical application areas where the SpaceWire SpW-RTC is well suited. Referring to figure 7 the SpW-RTC is used as a

Figure 7: Instrument Support Unit general block diagram.

separate analog acquisition board within the instrument support module. Measurements from temperature sensors, voltage and current sensors are typical HK parameters that will be accessible through the CAN bus or the SpaceWire links. The ICU may command and control the other instruments through the CAN bus.

#### 5. Conclusion

Overall, the modular architecture concept promoted by ESA and based on SpW interfaces and the development strategy adopted by ESA proved to be beneficial and fully applicable for the SpW-RTC development. Beside very specific applications driven by high data rates, the SpW-RTC design complies with very challenging On-Board computing and control needs.

ESA methodology for ASSPs validation is based on a set of selected alpha customers that will test the device in different context applications. For the SpW-RTC case, a community of scientific instrument designers related to ESA Bepi-Colombo mission has acquired the FPGA version of the SpW-RTC development kit and related tools. This has been done with the support of ESA to help these users for the implementation of their applications with the advantage of:

- Rapid prototyping

- Physically implementation of the algorithms, that concludes in a rapid execution of tasks

- Combine the tools of both hardware and software making the integration and validation phases easier and significant reduction in time-to-test and integration

The goal of the community is to assess the SpW-RTC device as common back-end candidate for most of Bepi-Colombo instruments. The benefit and the return of information of this community will pave the road of the SpW-RTC usage not only for Bepi-Colombo mission but to the following ESA programs XEUS, Cosmic Microwave Background Polarization Mapper (CMPM), to name a few of them.

Some of the most generic architectures using the SpW-RTC device for On-Board computing system have been presented. The goal of this survey was to summarize the ideas that emerge during its development as validation applications. The idea of parallel and pipelined architectures based on multiple SpW-RTC devices also emerged to solve problems that require higher level of computation. The related set will be forming fast processors for implementation of different tasks in payload processing. This type of architecture will need to be assessed and can constitute the basis of further work

#### **6. Reference Documents**

- [1]: SpaceWire Remote Terminal Controller, User Manual v1.7 (issued Feb 2007)

- [2]: SpaceWire Remote Terminal Controller datasheet v.5 (issued May 2007)

- [3]: "Integrated Development Tools Suite for the SpaceWire RTC ASIC"

W.Errico, J.Ilstad, A.Colonna, F.Bertuccelli

International Spacewire Conference 17-19 September, 2007 Dundee (Scotland)

[4]: "SpaceWire device driver for the remote terminal controller" A.Ferrer Florit, W.Gasti

International Spacewire Conference 17-19 September, 2007 Dundee (Scotland)

- [5]: SpaceWire Router Data Sheet Issue 2.0 August 18, 2006

- [6]: SpW-RTC Development Suite,

S.Habinc, J.Ilstad

International Spacewire Conference 17-19 September, 2007 Dundee (Scotland) [7]: TopNet demonstration

R.Vitulli, A.Ferrer Florit, J.Ilstad International SpaceWire Conference 17-19 September, 2007 Dundee (Scotland)